正常供货

正常供货改进的16位内核架构:采用1个程序存储器总线与3个数据存储器总线,支持并行访问指令和数据,单周期内可完成两次读操作和一次写操作,显著提升运算效率;

40位ALU:包含40位桶形移位器和两个独立40位累加器,支持高精度算术与逻辑运算。

17×17位乘法器:与40位专用加法器结合,实现单周期乘法/累加(MAC)操作,适用于滤波、FFT等算法;

CSSU单元:专为维特比算法优化,提升通信编解码性能;

主频与性能:100MHz时钟频率,执行速度达100MIPS(百万条指令/秒),满足实时信号处理需求;

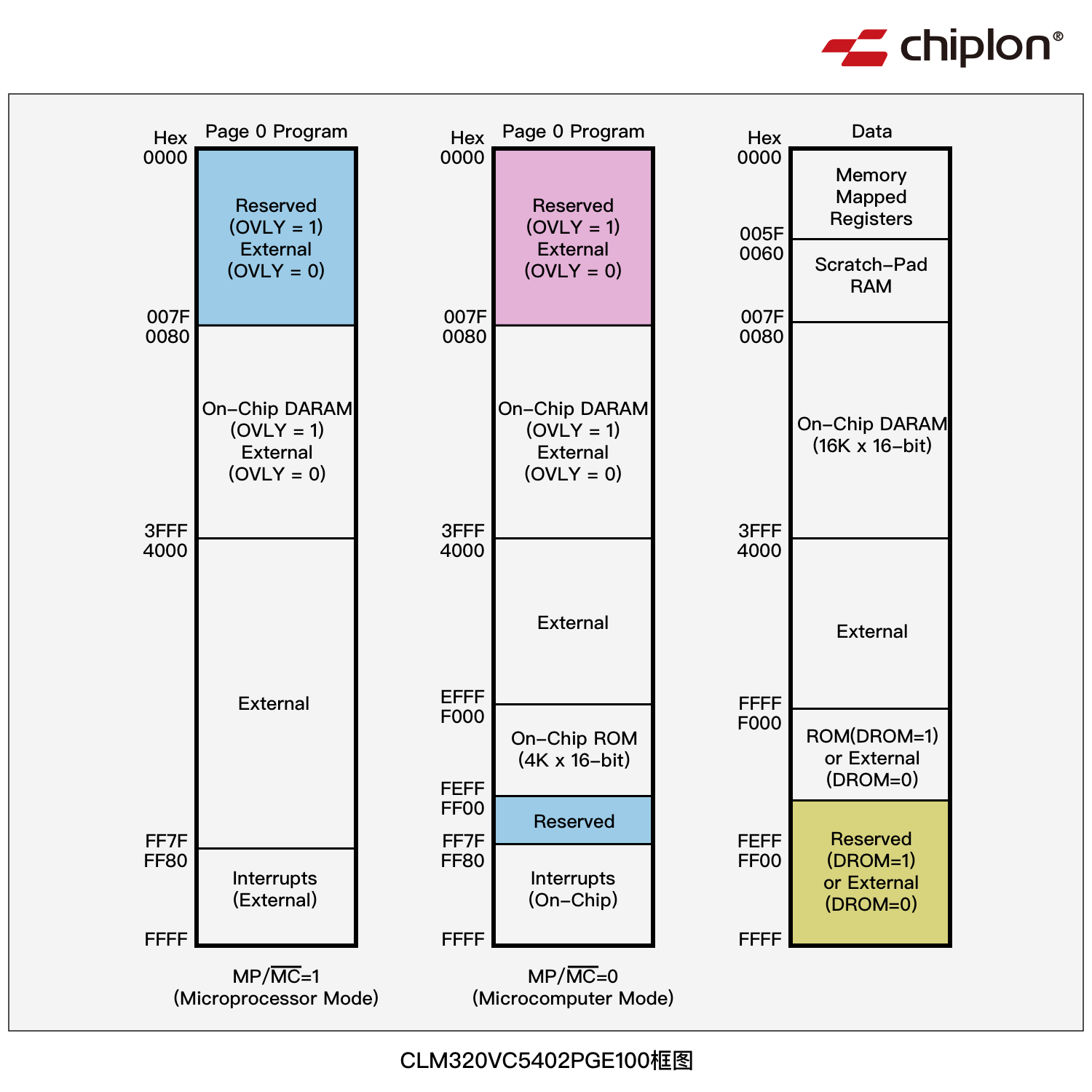

片上存储:32KB双端口RAM:支持程序与数据的高速存取;

8KB ROM:预存常用算法或启动代码,减少外部存储依赖;

扩展能力:支持最大1M×16位外部程序空间扩展,适应复杂应用场景;

多通道缓冲串口(McBSP):支持SPI、I²S等协议,可直接连接音频编解码器或通信模块;

增强型8位主机接口(HPI8):便于与主控处理器(如MCU)通信,简化系统集成;

DMA控制器:6通道DMA,实现数据高效传输,减轻CPU负担;

定时器与中断管理:内置两个16位定时器,支持精确时序控制;快速中断响应机制提升实时性;

双电压设计:核心电压1.8V,I/O电压3.3V,兼顾低功耗与兼容性;

低功耗模式:支持IDLE1/2/3三种休眠模式,动态调节功耗,适用于电池供电设备;

封装形式:LQFP-144(20×20mm),表面贴装设计,适用于高密度PCB布局;

工作温度范围:-40°C至100°C,适应工业与汽车电子严苛环境;

环保标准:符合RoHS无铅规范,满足环保要求;

仿真与调试:集成JTAG边界扫描接口,支持实时调试与代码烧录;

软件工具链:兼容的开发环境,提供算法库与硬件驱动支持。

CLM320VC5402是启珑微电子(Chiplon)匠心打造的一款高性能16位定点数字信号处理器(DSP)。它专为实时嵌入式应用场景量身定制,基于优化升级的16位内核架构,性能卓越,功耗极低。同时,其具备丰富的接口特性,可编程灵活性更是出类拔萃,在工业控制、医疗设备、通讯等关键领域,已然成为不可或缺的核心器件。值得一提的是,CLM320VC5402可实现直接Pin to Pin替代国际同类型产品,在替换过程中,无需在物理层或应用层进行设计更改(不需要做软件硬件修改)便能达成完全兼容替换,极大地降低了产品升级或替换的成本与难度。启珑微电子采用自主研发的先进测试方案,对每一个出厂产品进行严苛测试,确保产品性能不仅符合,甚至超越原始规格书标准。并且,该产品支持在工业级(-40℃ ~ 100℃)的宽泛温度范围内稳定工作,能够适应各种复杂恶劣的环境,为各类应用提供可靠保障 。

改进的16位内核架构:采用1个程序存储器总线与3个数据存储器总线,支持并行访问指令和数据,单周期内可完成两次读操作和一次写操作,显著提升运算效率;

40位ALU:包含40位桶形移位器和两个独立40位累加器,支持高精度算术与逻辑运算。

17×17位乘法器:与40位专用加法器结合,实现单周期乘法/累加(MAC)操作,适用于滤波、FFT等算法;

CSSU单元:专为维特比算法优化,提升通信编解码性能;

主频与性能:100MHz时钟频率,执行速度达100MIPS(百万条指令/秒),满足实时信号处理需求;

片上存储:32KB双端口RAM:支持程序与数据的高速存取;

8KB ROM:预存常用算法或启动代码,减少外部存储依赖;

扩展能力:支持最大1M×16位外部程序空间扩展,适应复杂应用场景;

多通道缓冲串口(McBSP):支持SPI、I²S等协议,可直接连接音频编解码器或通信模块;

增强型8位主机接口(HPI8):便于与主控处理器(如MCU)通信,简化系统集成;

DMA控制器:6通道DMA,实现数据高效传输,减轻CPU负担;

定时器与中断管理:内置两个16位定时器,支持精确时序控制;快速中断响应机制提升实时性;

双电压设计:核心电压1.8V,I/O电压3.3V,兼顾低功耗与兼容性;

低功耗模式:支持IDLE1/2/3三种休眠模式,动态调节功耗,适用于电池供电设备;

封装形式:LQFP-144(20×20mm),表面贴装设计,适用于高密度PCB布局;

工作温度范围:-40°C至100°C,适应工业与汽车电子严苛环境;

环保标准:符合RoHS无铅规范,满足环保要求;

仿真与调试:集成JTAG边界扫描接口,支持实时调试与代码烧录;

软件工具链:兼容的开发环境,提供算法库与硬件驱动支持。

工业测量与自动化

汽车电子与安全系统

通讯与多媒体处理

医疗设备

消费电子与嵌入式控制